| 課題番号    | Q18T-01                                                                                          |  |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 課題名(和文) | FPGA を用いたマルチレベルモジュラーコンバータの高精度ディジタル制御手法の開発                                                        |  |  |  |  |  |  |  |

| 課題名(英文) | Development of high-precision digital control method of multi-level modular converter using FPGA |  |  |  |  |  |  |  |

|         | 所属(学部,学科・学系・系列,職位)                                                                               |  |  |  |  |  |  |  |

| 研究代表者   | 未来科学部 ロボット・メカトロニクス学科 教授                                                                          |  |  |  |  |  |  |  |

|         | 氏名 横山 智紀                                                                                         |  |  |  |  |  |  |  |

| 共同研究者   | 所属(学部、学科・学系・系列、職位)                                                                               |  |  |  |  |  |  |  |

|         |                                                                                                  |  |  |  |  |  |  |  |

|         | 氏名                                                                                               |  |  |  |  |  |  |  |

|         | 所属(学部、学科・学系・系列、職位)                                                                               |  |  |  |  |  |  |  |

|         |                                                                                                  |  |  |  |  |  |  |  |

|         | 氏名                                                                                               |  |  |  |  |  |  |  |

|         | 所属 (学部、学科・学系・系列、職位)                                                                              |  |  |  |  |  |  |  |

|         |                                                                                                  |  |  |  |  |  |  |  |

|         | 氏名                                                                                               |  |  |  |  |  |  |  |

# 研究成果の概要 (和文)

現在,次世代の大容量電力変換器として,モジュラーマルチレベルコンバーター(MMC)が注目されている.MMC の制御には,一般に PI 制御が広く使用されている.一方,モデルベースのディジタル制御方式については,デッドビート制御およびモデル予測制御が適用されている.本研究では,MMC の PWM ホールド手法を使用した疑似マルチレートデッドビート(QMDB)制御を提案した.FPGA ベースのハードウェアコントローラーを適用することで,瞬時の制御計算を実行できるため,理想的なディジタル制御フィードバックシステムが実現できる.提案手法の有効性を,シミュレーションと実験により示した.

### 研究成果の概要(英文)

Currently, modular multi-level converters (MMC) are attracting attention as the next generation of high-capacity power converters. For the control of the MMC, PI control is widely used. On the other hand, the deadbeat control and/or the model predictive control was applied as for the model based digital control method, and the superior characteristics were obtained. In this paper, a quasi multi-rate deadbeat (QMDB) control for MMC was proposed using a PWM hold method. Applying FPGA based hardware controller, instantaneous control calculation can be carried out which result in the ideal digital control feedback system. The advantages of the proposed method were verified through simulations and experiments.

#### 1. 研究開始当初の背景

近年.大容量の電力変換器として様々なマルチ レベル変換器の研究が進められている.マルチレ ベル変換器の中でも、モジュラー・マルチレベル変 換器(MMC)が注目されている.MMC は,低耐圧か つ高速のスイッチング素子を使用できるため,ス イッチング素子の損失低減および高周波化が可 能である.また,マルチレベル波形を得られること から,フィルタを小さくすることができ,大規模シ ステムの小型化が実現できることから,太陽光発 電や風力発電などの大規模な発電システムへの 適用が注目されている.現在,MMC に関する様々 な研究がされており、多くの回路構成や制御手法 が提案されている.一般的な制御手法として,平均 値制御やバランス制御などの PI 制御やコスト関 数を用いた電流制御を行うモデル予測制御 (WMPC)が多く採用されている(1)(2).MMC の制御 では、主回路の制御に加えて、カスケード接続され た各セルに含まれる直流コンデンサ電圧Vcの制御 が必要となる.従来の制御手法である平均値制御 やバランス制御などの PI 制御を用いる場合,パラ メータ変動に対する応答性や指令値への追従性 などが問題となる.

### 2. 研究の目的

これらの問題に対し、従来の研究では、2 レベルインバータや NPC 変換器に対してデッドビート制御の適用が提案されており、良好な応答を確認することができた(3)(4).本研究では、疑似マルチレートデッドビート(QMDB)制御を適用することにより、パラメータ変動に対する応答性の向上と指令値への追従性に焦点を当てた、提案するデッドビート制御は、正確な離散モデルに基づいて設計されている。離散モデルを導出するために、パルス波形の面積に注目した、PWM ホールド手法を使用している。MMCにPWMホールド手法を採用することで、新しい離散モデルを提案している。主回路と直流コンデンサ電圧の制御が必要となるMMCの制御性能を向上させるため、PWMホール

ド手法による離散化モデルを用いたデッドビート制御方式を提案する.サンプリングや制御演算の遅延の影響を回避するため,全ての制御演算はFPGA を搭載したコントローラにより実行される.全ての制御演算は数 $\mu$ 秒で演算でき,理想的な高速デジタルフィードバックシステムを実現できる.

### 3. 研究の方法

提案手法を検証するため,従来手法と比較して シミュレーションと実験を行い,提案手法の利点 を検証する.

- (1) 回路シミュレータ(PSIM)を用いたシミュレーションによる検証を行う.制御対象のシミュレーションを実装し、PI 制御と提案手法(QMDB制御)を比較する.

- (2) 実機システムを構築し,実機による検証を 行う.FPGA コントローラと制御対象とな る MMC変換器の実験環境を構築し,FPGA コントローラに VHDL を実装する.各種負 荷条件(定格抵抗負荷,負荷変動,非線形負 荷)による実機検証を行う.

### 4. 研究成果

MMC は、主に小型化や応答性に関する研究が 進められており、回路構成や制御手法によるアプローチにより改善が行われている。今回は、高精度 ディジタル制御手法を用いて MMC の応答性を向上させることにより、実機システムの小型化を目指す.

### (1)制御手法

Fig.1 に 9 レベル単相 MMC フルブリッジ回路を示す.主回路は,上下各 4 つのチョッパ回路 (セル)とバッファリアクトル $L_b$ により構成される.各セルをカスケード接続し,バッファリアクトル $L_b$ と接続する.動作原理は,各セルの直流コンデンサ電圧 $V_c$ を均一に保ち,電圧指令値 $\Delta T$ に

よって決定されることにより、階段状のマルチレベル波形が生成される.次に、バッファリアクトル $\mathbf{L}_b$ とフィルタリアクトル $\mathbf{L}_f$ 、フィルタコンデンサ $\mathbf{C}_f$ を介して、交流電圧 $\mathbf{V}_0$ が生成される.

Fig. 1 MMC9 レベル単相フルブリッジ回路

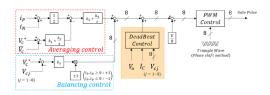

Fig.2 に提案手法の制御ブロック図を示す.従来の PI 制御手法である平均値制御②とバランス制御②にデッドビート制御を加える手法を提案する.

Fig. 2 提案制御手法ブロック図

## (2)モデリング

### ① マルチレベル PWM 波形

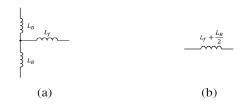

本節では、9 レベルの MMC 単相フルブリッジ回路のモデリング手法について述べる.インバータ出力電圧 $V_p$ は通常、バッファリアクトル $L_b$ の成分を含むことにより、Fig.3(a)のようなひし形の波形となる.ここで、Fig.4(a)に示したバッファリアクトル $L_b$ とフィルタリアクトル $L_f$ を Fig.4(b)のように等価回路として考慮することで、Fig.3(b)のような出力パルス波形と仮定でき、提案するパルスモデルを組むことができる.

Fig. 3  $L_b$ と $L_f$ を含むインバータ電圧波形 (a)  $L_b$ を含む波形 (b)等価回路を含む波形

Fig. 4 モデリングのための $L_b$ と $L_f$ (a)実回路 (b)等価回路

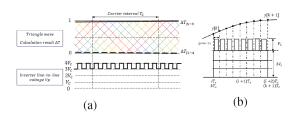

Fig.5,Fig.6 に MMC の PWM 方式を示す. セル数に応じて位相を変化させた三角波を 用いる変調方式を用いる.MMC の PWM 制御 方法として,各セルの三角波キャリア波形が 使用される.PWM 制御は,各セル数分の三角 波キャリア波形と制御入力*ΔT* をそれぞれ比 較することによって制御される.

Fig. 5  $\Delta T < 1/8$ ,  $\Delta T > 7/8$ の PWM モデル (a)操作量とインバータ電圧 (b)モデリング

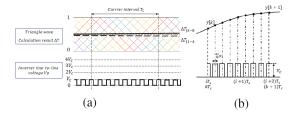

Fig. 6  $3/8 \le \Delta T \le 5/8$ の PWM モデル (a)操作量とインバータ電圧 (b)モデリング

従来の PWM ホールド手法では、サンプリン グ周期 $T_s$ とキャリア周期 $T_c$ が等しく、1 キャリア内に 1 つパルスが出力する、中央パルスモデル

を適用していた.Fig.5(a)は,操作量ΔTが 1/8 以 下と 7/8 を超える場合を示している.この場合, サンプリング周波数fsを 8 倍にすることによ り、1サンプリング周期内に中央パルスモデルを 採用することができる.Fig.6(a) は、操作量 $\Delta T$ が 3/8 以上かつ 5/8 以下の場合を示している.こ の場合,サンプリング周期内の両端でパルスが2 つに分割する.この場合,各パルスを1サンプリ ング周期内で合計することにより,中央パルス モデルを採用することができる.MMC では,直 流電源Eを交流に変換するのではなく,各セルの コンデンサ電圧Vcを均一に保つことで,任意の 交流を出力しているため,直流電源Eの値は出力 電圧Voに影響を及ぼさない.このことから も,Fig.5(b)の出力パルスの領域を求めるための 演算には、直流電源Eではなく各セルのコンデン サ電圧Vcを用いる必要がある.パルスの高さは  $V_{c,}$ パルス幅は( $\Delta T[k]$ )/8 であり,1 キャリア内の パルス領域は、パルスが8つある、2レベルイン バータの操作量 $\Delta T$ が  $\mathbf{MMC}$  の操作量 $\Delta T$ と等し い場合,2レベルインバータの出力パルス内の領 域は、1キャリア内のMMCの出力パルス領域に 等しいといえる.Fig.6(b)についても同様に考え ることができる.したがって,従来の2 レベルイ ンバータにおいて用いていたデッドビート制 御則を MMC に適用することができる.

#### ② 疑似マルチレートデッドビート制御

Fig.1の主回路モデルから,連続時間状態方程式は(1)となる。

$$x(k) = \begin{bmatrix} \dot{v}_o \\ \dot{V}_o \end{bmatrix}, A = \begin{bmatrix} 0 & 1 \\ -\frac{1}{LC} & -\frac{1}{RC} \end{bmatrix}, B = \begin{bmatrix} 0 \\ \frac{1}{LC} \end{bmatrix}$$

(1)

離散時間系のPWMホールド手法に基づく状態方程式は以下のようになる.演算内で用いるVcj(j=1~8)は,各セルのコンデンサ電圧をフィードバック値として用いる.

$$\begin{split} x(k+1) &= A_d x(k) + B_d u(k) \\ x(k) &= \left[ \begin{array}{c} V_o(k) \\ \dot{V}_o(k) \end{array} \right], A_d = e^{ATs}, B_d = e^{\frac{ATs}{2}} B_c V_{cj} \end{split}$$

(2)より,2 時点先の PWM パルス幅を求めると、(3)のマルチレート制御式が求まる.

$$\begin{split} x(k+2) &= A_d x(k+1) + B_d u(k+1) \\ &= A_d^2 x[k] + [A_d B_d \quad B_d] \left[ \begin{array}{c} u[k] \\ u[k+1] \end{array} \right] \end{split} \tag{3}$$

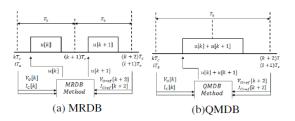

Fig.7(a)(b)にマルチレートデッドビート制御 と疑似マルチレートデッドビート制御の PWM パルスモデルを示す。

Fig. 7 離散モデルのための PWM パルスパター

(a)MRDB (b)QMDB

本研究では、提案手法として疑似マルチレートデッドビート制御を適用する.(4)と置き換え、(5)をu(i)について求める.

$$\begin{bmatrix}

u[k] \\

u[k+1]

\end{bmatrix} = u(i)$$

(4)

$$x(i+1) = A_n x(i) + B_n u(i)$$

$$\tag{5}$$

$$u(i) = B_n^{-1}x(i+1) - B_n^{-1}A_nx(i)$$

(6)

Fig.7(b)に示したように, u(k)とu(k+1)を 足し合わせ,1キャリア分の PWM パルスモデル とする.以上より,提案手法の制御式が求まる.

### (3) シミュレーション結果

PI 制御と提案手法(QMDB 制御)のシミュレーションを行った.条件は,定格負荷と負荷変動とする.パラメータは Table.1 に示す.

| la | b | le | 1 |   | P | a  | ra | m | e   | te  | ľ |

|----|---|----|---|---|---|----|----|---|-----|-----|---|

| Ia | U | le | ı | ٠ | Г | d. | Γd | П | IC. | lC. | I |

| Condition                 | PI               | QMDB         |  |

|---------------------------|------------------|--------------|--|

| Sampling frequency $f_S$  | 80[kHz]          |              |  |

| Carrier frequency $f_C$   | 10[kHz]          |              |  |

| Nominal capacity P        | 500[VA]          |              |  |

| Output voltage $Vo_{rms}$ | 100[V]           |              |  |

| Operating frequency F     |                  | 50[Hz]       |  |

| DC power supply $E_{DC}$  | 200[V]           |              |  |

| Capacitor voltage $V_C$   | 50[V]            |              |  |

| Buffer inductor $L_b$     | 1[mH](3.14%Z)    |              |  |

| Filter inductor $L_f$     | 182[μH](0.572%Z) |              |  |

| Filter capacitor $C_f$    | 30               | [μF](9.42%Z) |  |

| Gain 1 $K_1$              |                  | 0.5          |  |

| Gain 2 K <sub>2</sub>     | 80               |              |  |

| Gain 3 $K_3$              | 1.0              |              |  |

| Gain 4 K <sub>4</sub>     | 640              |              |  |

| Gain 5 K <sub>5</sub>     | 0.125            |              |  |

|                           |                  |              |  |

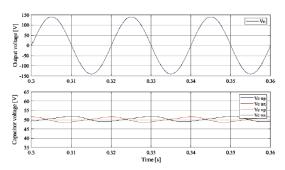

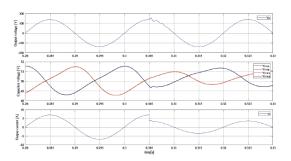

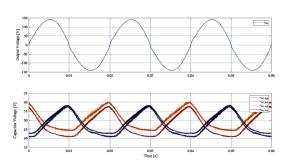

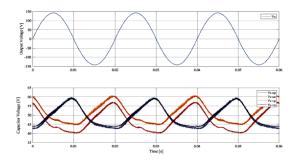

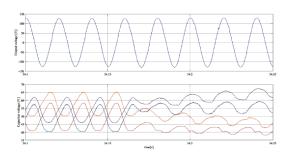

Fig.8 と Fig.9 は,PI 制御と QMDB 制御の定格負荷時の出力波形,Fig.10 と Fig.11 は,負荷変動時の出力波形を示している.Table.2 より,提案手法によって定格負荷時における THD を抑えることができている.また,負荷変動時における出力電圧指令値へ追従するまでの整定時間においても,提案手法により応答性の改善を確認できた.

Fig. 8 出力波形(PI 制御:定格抵抗負荷)

Fig. 9 出力波形(QMDB制御:定格抵抗負荷)

Fig. 10 出力波形(PI 制御:負荷変動)

Fig. 11 出力波形(QMDB 制御:負荷変動)

Table 2. Simulation result

| Control Method | THD[%] | SSE[%] | Settling time[ms] |

|----------------|--------|--------|-------------------|

| PI             | 4.65   | -1.07  | 5.0               |

| QMDB           | 0.860  | -0.449 | 1.0               |

# (4) 実験結果

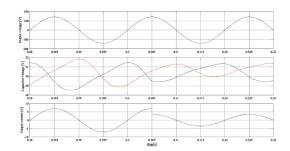

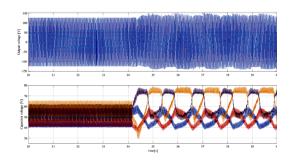

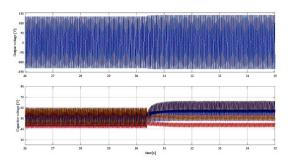

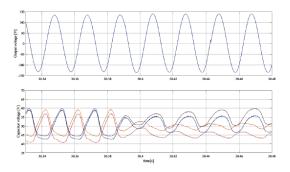

シミュレーションと同様の条件で実験検証を行った.Fig.12 と Fig.13 は PI 制御と QMDB 制御の定格負荷時の出力波形を示している.Fig.14 と Fig.15 は,負荷変動時の出力波形を示している.また,Fig.16 と Fig.17 に,拡大波形を示す.Table.3 を見ると,提案手法では PI 制御手法と比べて,THD が低減していることから.出力電圧の追従精度の改善を確認できた.

Fig. 12 出力波形(PI 制御:定格抵抗負荷)

Fig. 13 出力波形(QMDB制御:定格抵抗負荷)

Fig. 14 出力波形(PI 制御:負荷変動)

Fig. 15 出力波形(QMDB 制御:負荷変動)

Fig. 16 出力波形(PI 制御:整流器負荷)

Fig. 17 出力波形(QMDB制御:整流器負荷)

Table 3. Experimental result

| Control Method | THD[%] | SSE[%] |  |

|----------------|--------|--------|--|

| PI             | 4.17   | 1.33   |  |

| QMDB           | 1.28   | 1.27   |  |

### (5)まとめ

MMC 単相フルブリッジインバータの PWM ホールド手法に基づくデッドビート制御手法 (QMDB 制御)を提案し、シミュレーションおよび 実験により有効性を検証した。定常時の応答に関して、高周波成分と偏差を減らすことができた。負荷変動時の制御精度は、QMDB 制御を用いることで改善することができる.その結果,提案手法は定常特性と過渡特性の両方の制御性能が良好であることが確認された.応答性や THD の向上により、LC フィルタの小型化に関して有用性が望める.

## 5. 主な発表論文等

(研究代表者,共同研究者には下線)

〔学会発表〕(計 3件)

- ① 金井なつみ, 栗田将伍, 横山智紀, "MMC 変換器における疑似マルチレートデッドビート制御の検証", 電気学会産業応用部門大会, 2019年8月22日, 長崎大学

- ② Natsumi Kanai, Shogo Kurita, Takashi Ando, <u>Tomoki Yokoyama</u>, "A Study of Quasi Multi-rate Deadbeat Control for Single-

Phase Modular Multi-level Converter", S2PC, 2019 年 10 月 26 日,富士電機豊田工 場

③ Natsumi Kanai, Shogo Kurita, Takashi Ando, <u>Tomoki Yokoyama</u>, "A Study of Quasi Multi-rate Deadbeat Control for Modular Multi-level Converter using FPGA based Hardware controller", IFEEC, 2019 年 11 月 26 日, シンガポール